baysis3 3.3v, 5v 동작

가운데 박혀있는 칩이 xc7a35tcpg236-1

조합논리회로 : 논리곱AND, 논리합OR, 논리 부정NOT의 세 가지 기본 논리회로를 조합하여 구성한 논리회로

조합논리회로는 입력변수, 논리 게이트 그리고 출력변수로 구성

HDL : 언어로 회로설계, Verilog, VHDL로 구성

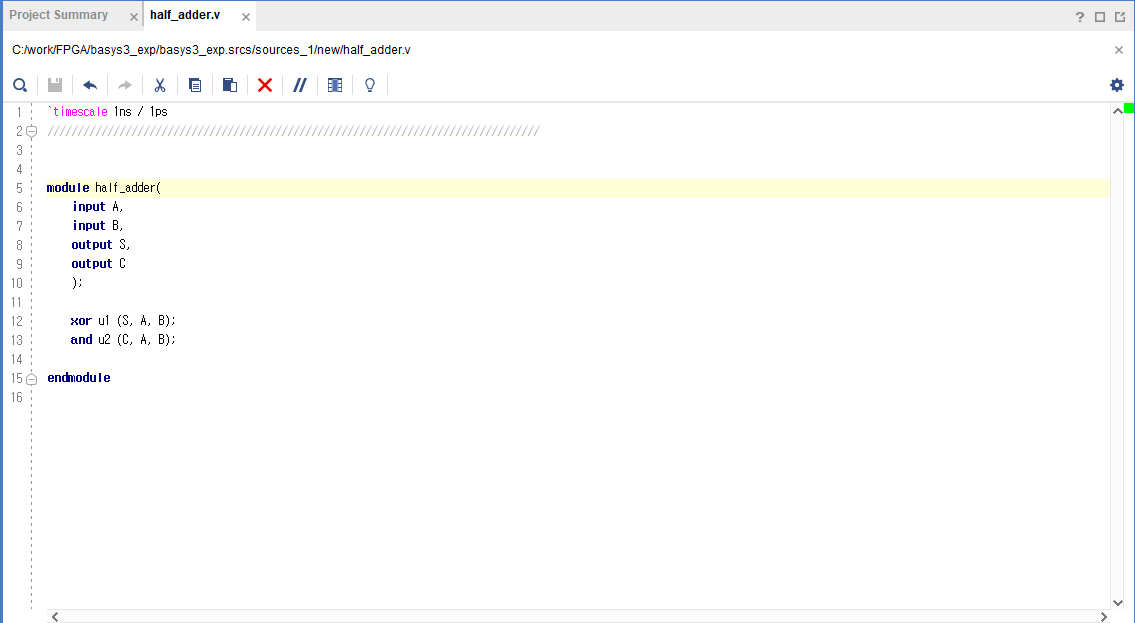

반가산기 (Half Adder)

Half Adder는 xor게이트와 and게이트로 구성되어있다.

xor은 A, B의 값이 다를 때 1을 출력한다.

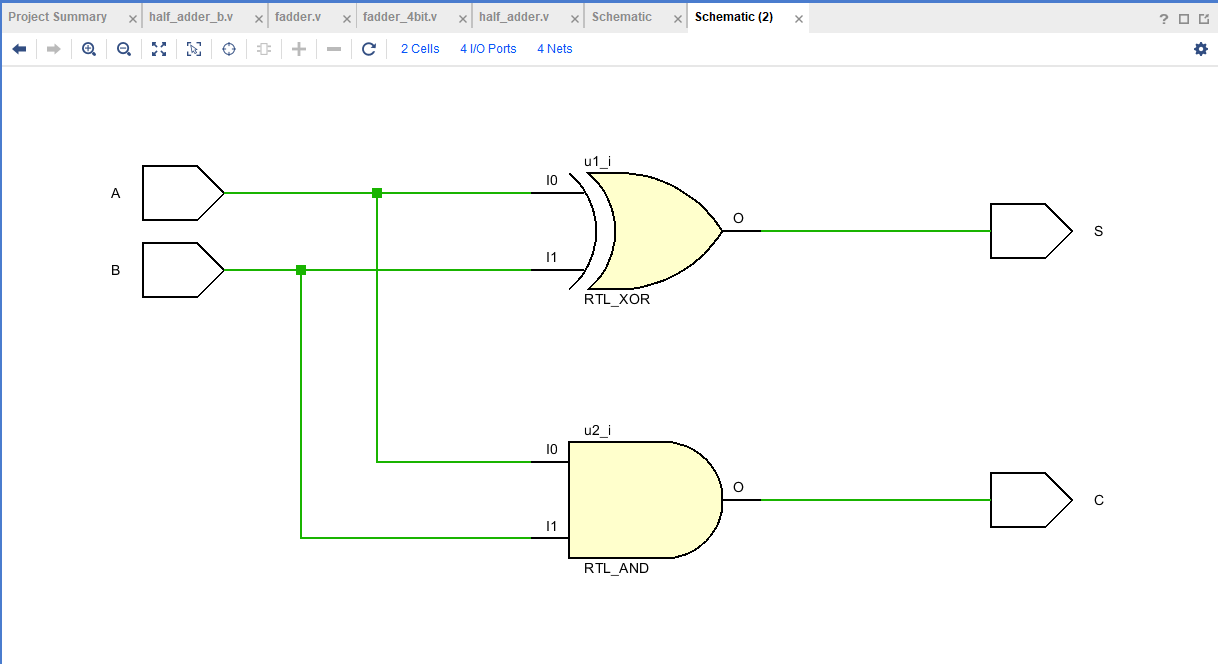

Half Adder의 schematic

xor 게이트는 출력이 앞, 입력이 뒤에 온다. S 출력, A, B 입력

and 게이트도 출력이 앞, 입력이 뒤에 온다. C 출력, A, B 입력

Schematic

HLS라고 함

(High Level Synthesis)

S 는 xor의 진리표와 같은 결과가 나온다.

C는 and의 진리표와 같은 결과가 나온다.

전가산기 (full-adder)

입력이 3개, 반가산기(Half-Adder) 2개, or게이트를 이용하여 구성

half_adder라는 모델을 사용해서 ha0를 만들겠다는 뜻

ha0의 A는 fadder의 A입력, B는 fadder의 B입력, S는 s0, C는 c0

ha1의 A는 s0, b는 Cin, S는 S, C는 c0

인스턴스를 만들면 ha0, ha1 같이 만들어짐.

ha0, ha1은 인스턴스 명, 가운데 모듈 명, 맨 끝 파일 명

fadder의 신호

병렬가감산기(parallel-adder/ subtracter)

병렬가산기 : 전가산기 여러 개를 병렬로 연결한 회로

A, B, S는 4bit

Bus 선택 후 MSB를 3으로 둬 0~3 4bit

[3:0] 은 0~3까지 4bit를 정의해주는 것

지금까지는 구조적 모델링

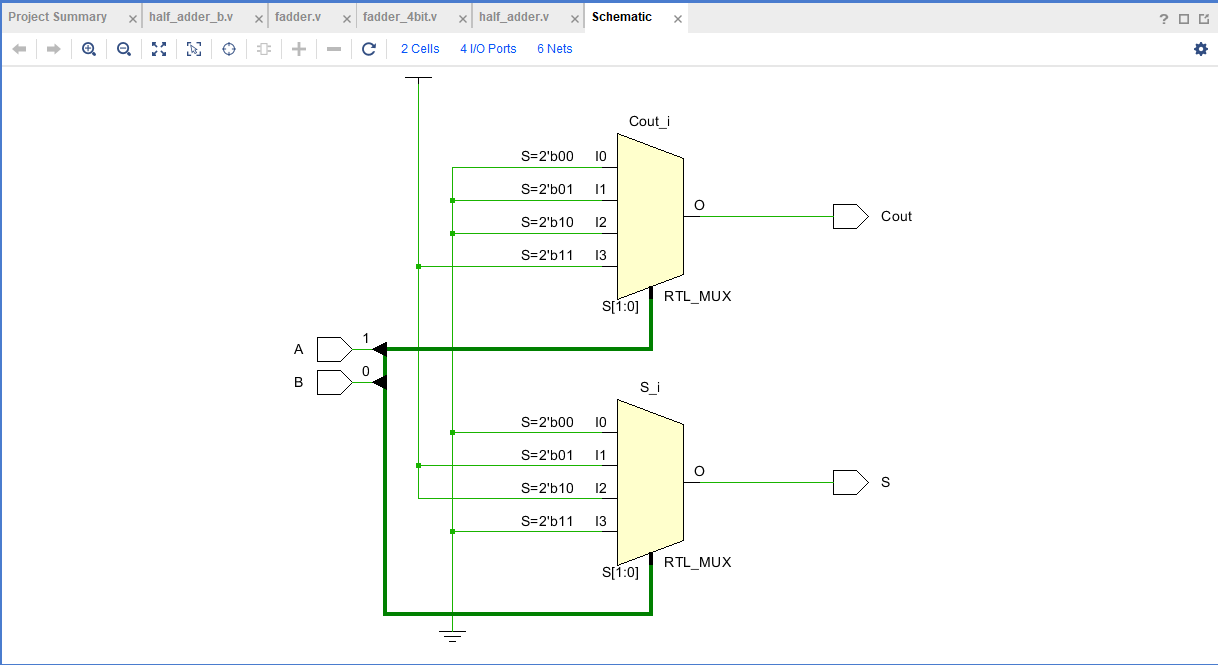

지금부터는 동작적 모델링

always @는 A와 B의 값을 보겠다는 것

전부 보고싶으면 A or B 자리에 *넣음

값이 바뀌면 case문 안이 실행됨

begin과 end를 사용해 블럭을 만든다.

case문에는 begin, end 사용 안함.

Verilog는 2가지 형태가 있다. wire, reg(레지스터형(메모리형태) 기본자료형)

A,B앞에 아무것도 없는건 디폴트가 wire

2가 앞에 있는건 2bit짜리 라는 것.

동작하는 것은 똑같음.

S=2'b00 ~2'b11까지 다 메모리.

2'b00 일 때, Cout = 0, S = 0

2'b10 일 때, Cout = 0, S = 1

2'b01 일 때, Cout = 0, S = 1

2'b11 일 때, Cout = 1, S = 0

데이터 플로우 모델링

assign문은 wire

assign문에서의 = 는 선을 연결한다.

동작적 모델링 (always @)문도 데이터플로우 모델링이 가능하나 assign이 없고 reg를 사용해야한다.

assign을 사용한 데이터 플로우 모델링과 always@문을 사용한 데이터 플로우 모델링의 신호 결과값이 같음을 확인할 수 있다.

FPGA로 만들건지 ASIC으로 만들건지에 따라 회로구성이 달라진다.

비교기

2진 비교기 : 두개의 2진수의 크기를 비교하는 회로

not(Bbar, B)로 B에 not을 대입

not(Abar, A)로 A에 not을 대입

equal = A와 B가 같을 때 1이 출력된다.

bigger = A가 B보다 클 때 1이 출력된다.

less = A가 B보다 작을 때 1이 출력된다.

'Verilog' 카테고리의 다른 글

| Verilog 레지스터 (0) | 2023.04.26 |

|---|---|

| Verilog 멀티플렉서, BCD 변환기, 플립플롭 (0) | 2023.04.19 |

| Verilog 인코더, 디코더, 7세그먼트, 멀티플렉서 (0) | 2023.04.18 |

| Verilog 3일 특강 2 (0) | 2023.04.17 |

| Verilog 3일 특강 1 (0) | 2023.04.13 |