한달 반으로 예정되어있던 베릴로그가 잠시 3일의 특강을 가지고 시작했다.

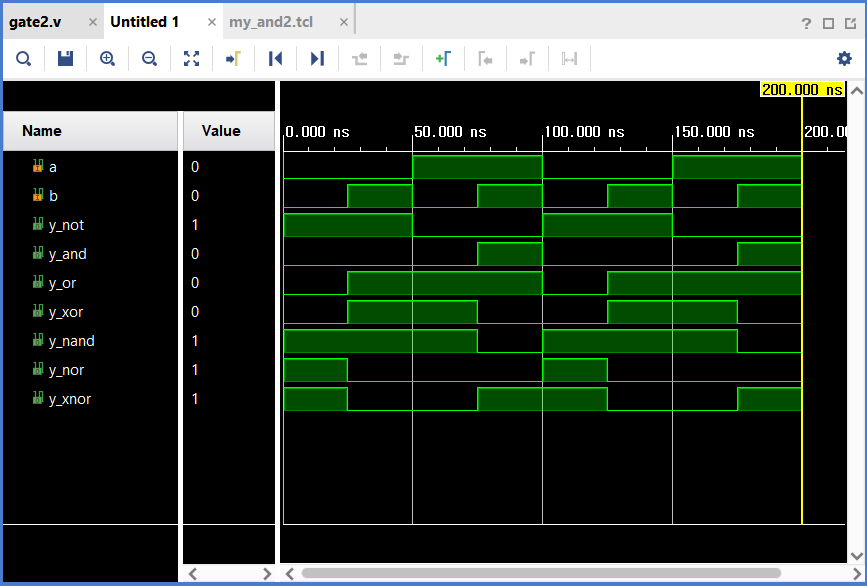

not : ~ a

and : a & b

or : a | b

xor : a ^ b

nand : ~(a & b)

nor : ~(a | b)

xnor : ~(a ^ b)

xor 과 xnor 은 헷갈리니 따로 사진첨부

xor은 배타적 논리합으로 둘 중 하나만 참일 경우 판단하는 논리 연산

입력값이 동일하면 1을 출력하고 다르면 0을 출력한다.

비교 게이트나 일치 확인 게이트라고도 부른다.

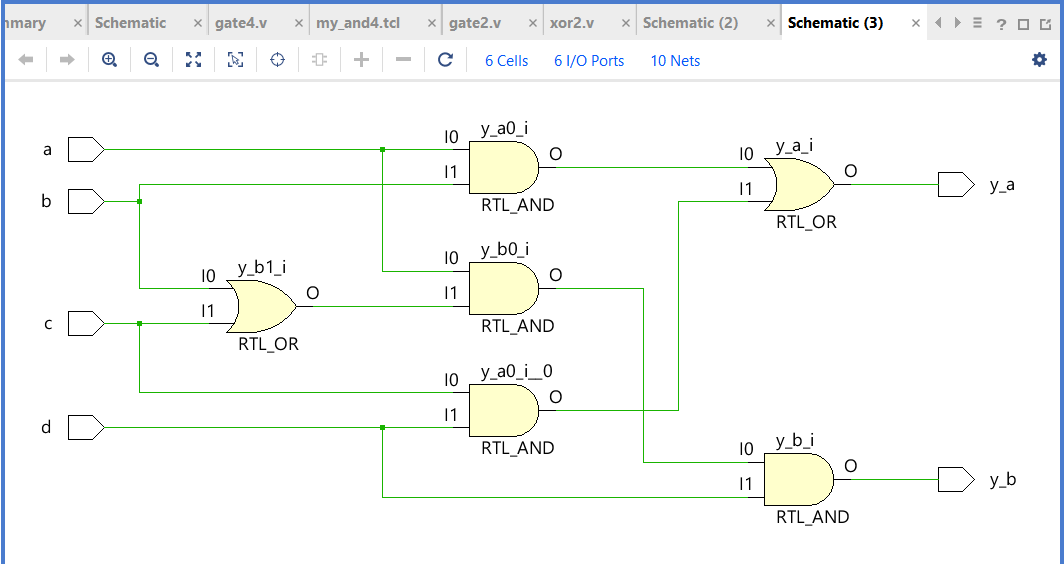

위 코드를 실행했을 때 schematic

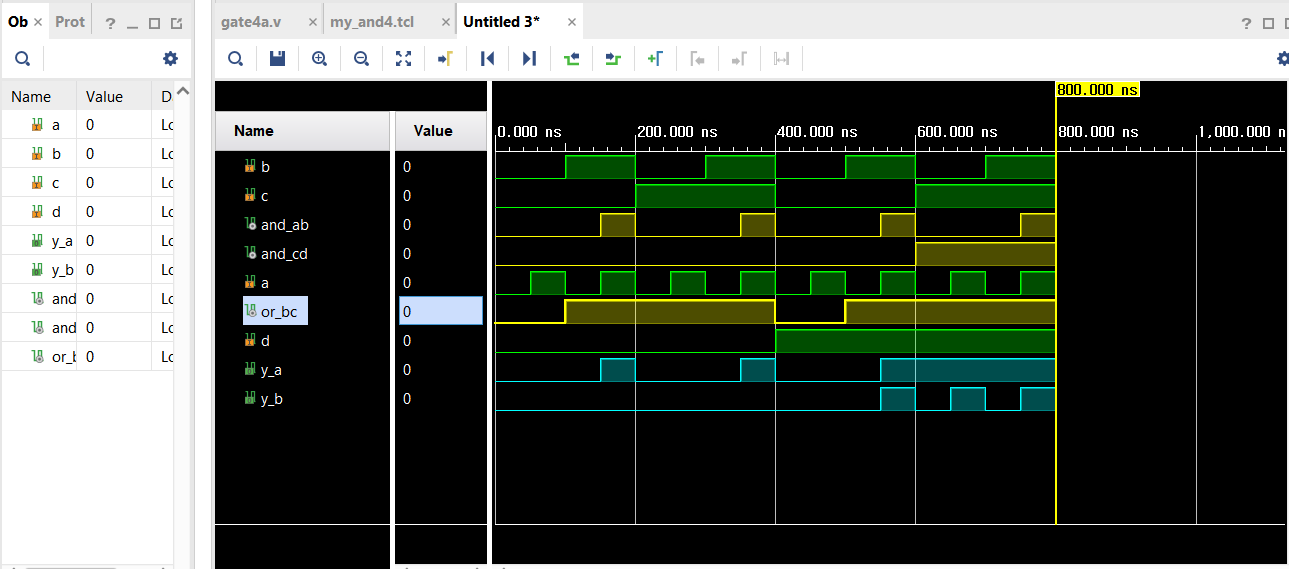

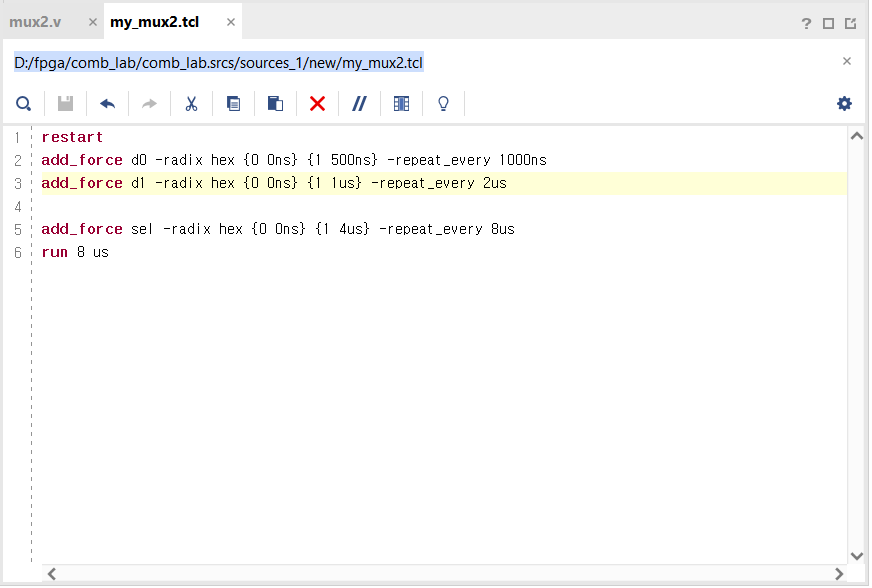

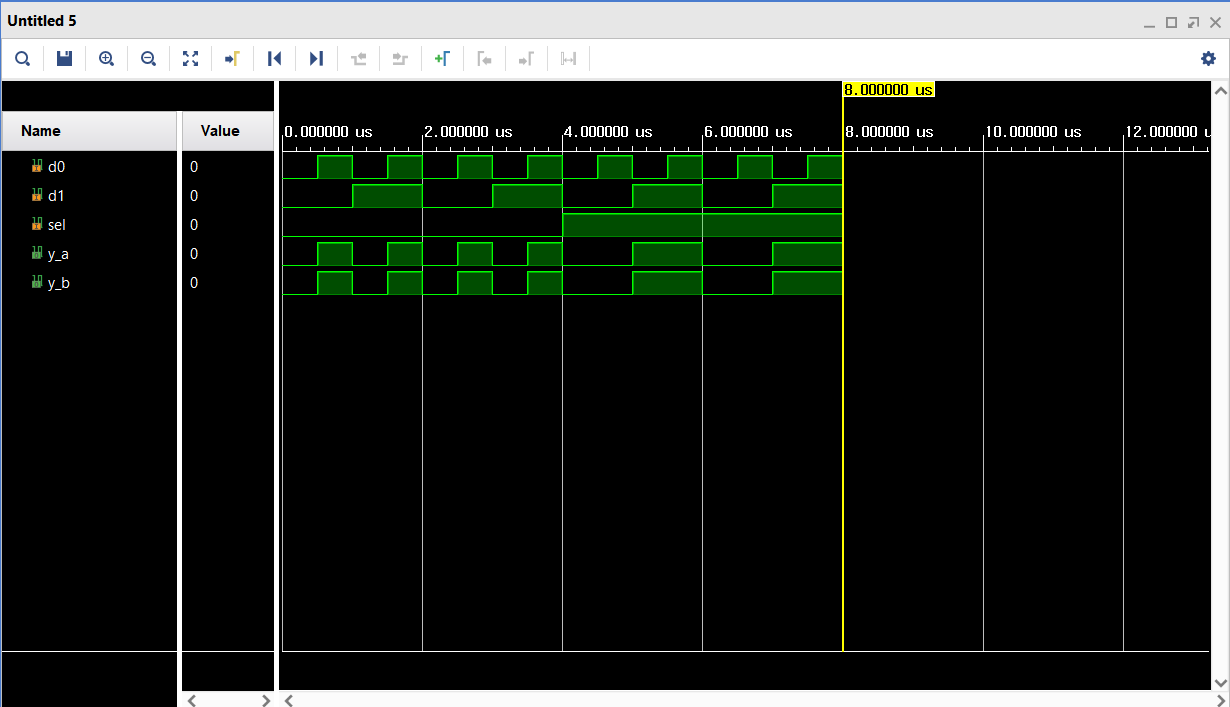

tcl 파일을 불러와 신호값을 처리하는 과정

not 은 ~a 였으므로 a의 신호와 정반대

and는 a, b의 신호가 1일 때 1을 출력

or은 a, b 중 1개만 1이어도 1을 출력

xor은 a, b 가 같은 값일 경우엔 0 둘 중 하나가 참이면 1

nand는 둘 다 1의 값이 아닐 경우 1 출력

nor은 둘다 참이 아닐 경우 1출력

xnor은 0이든 1이든 값이 같을 경우 1 출력

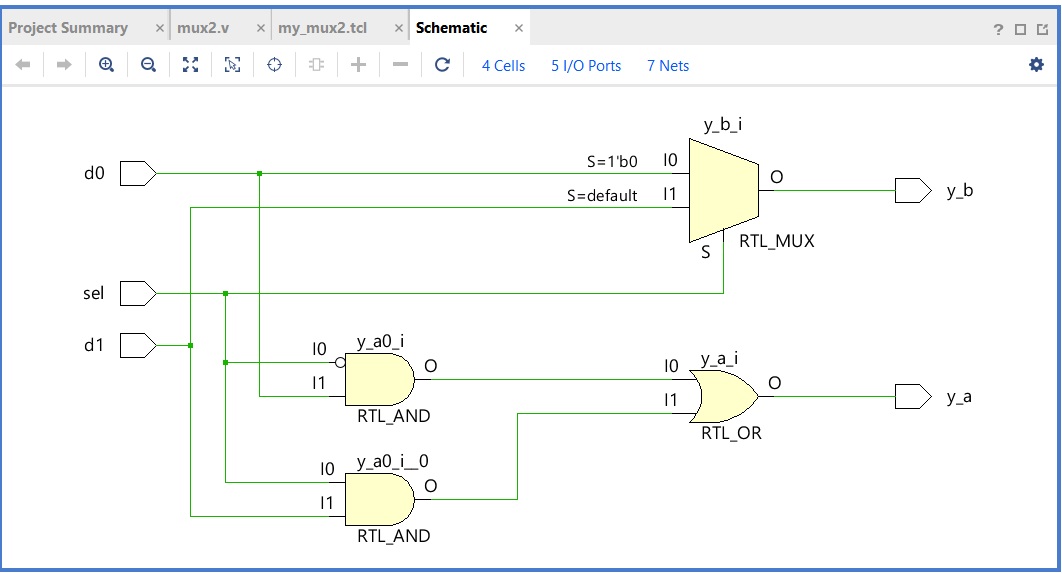

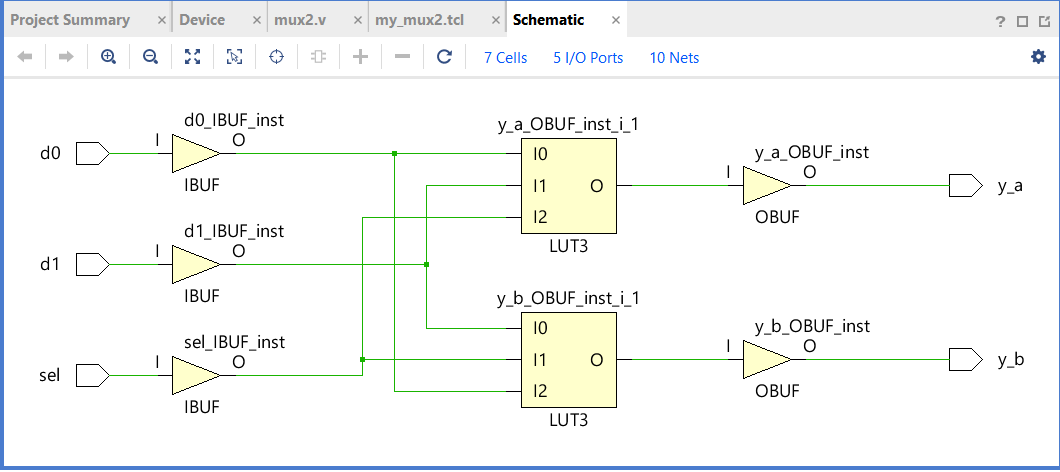

SYNTHESIS에서 Schematic 클릭하면 아래와 같이 나옴

LUT : look up table 약자

1~6을 기본 라이브러리로 사용

1번, 2번 방에 넣는 수를 달리해 버퍼가 인버터 역할을 할 수 있음

LUT6까진 CLB에서 출력이 4개가 되지만 출력은 1개만 사용

배선 delay 고정

CLB 1개로 LUT6까지 가능

LUT7부턴 클럭 1개 더, 속도가 떨어짐

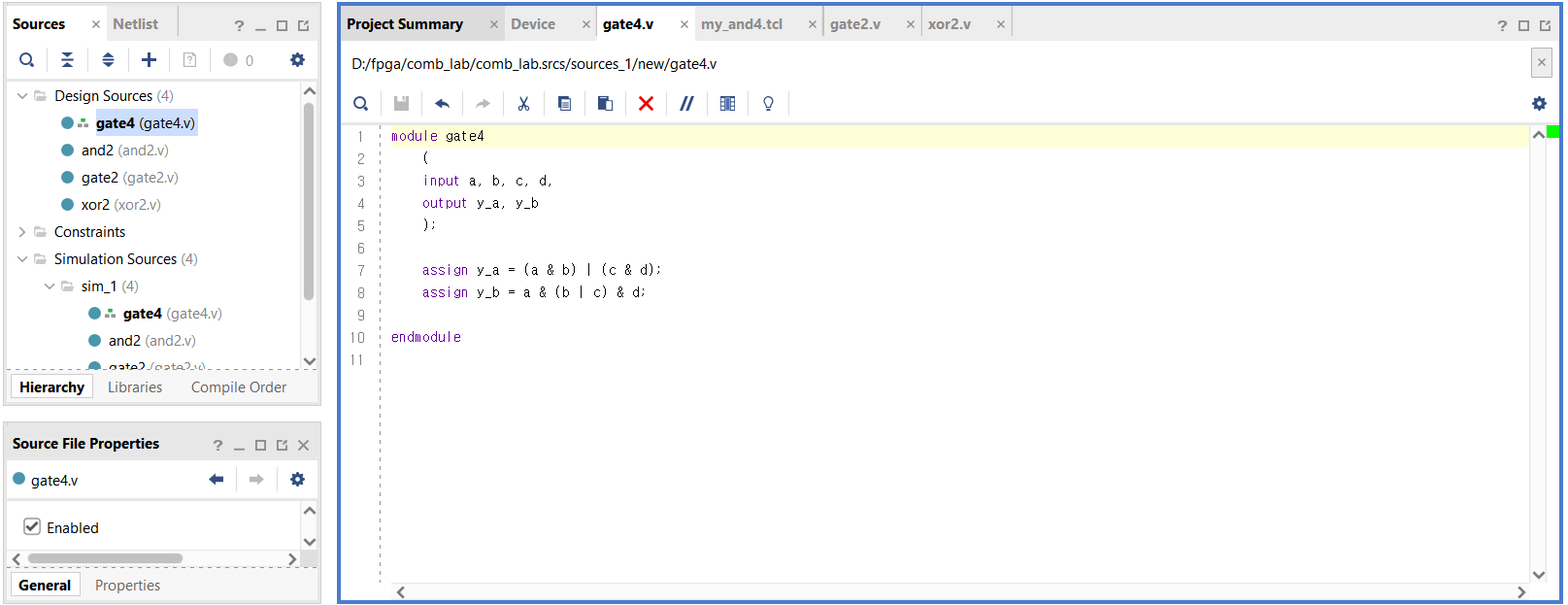

입력 4개를 통해 회로 구성

a & b 와 c % d를 |를 사용해 y_a를 구성하고

a & (b | c) & d로 y_b를 구성

위 코드를 실행하여 schematic을 실행한 결과

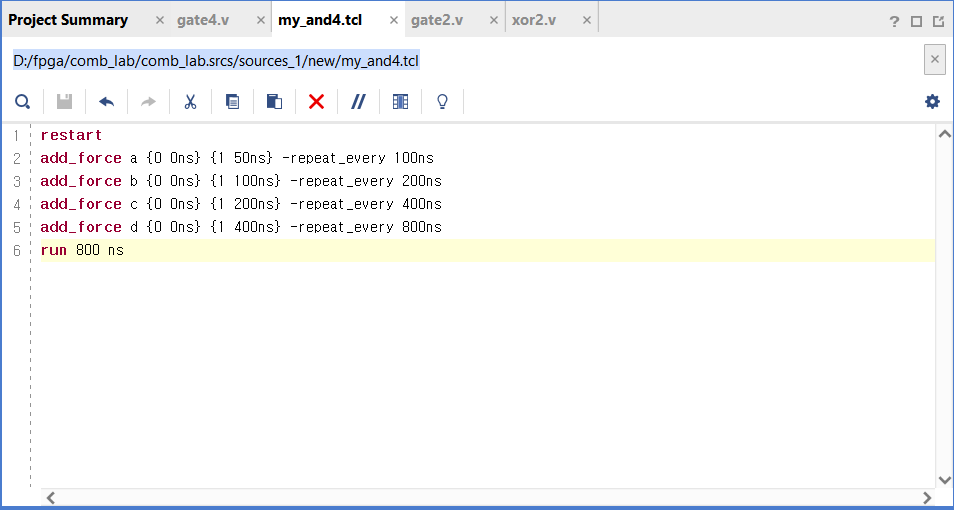

a의 신호를 0의 0ns부터 시작하여 50ns마다 1의 신호를 100ns마다

b의 신호를 0의 0ns부터 시작하여 100ns마다 1의 신호를 200ns마다

c의 신호를 0의 0ns부터 시작하여 200ns마다 1의 신호를 400ns마다

d의 신호를 0의 0ns부터 시작하여 400ns마다 1의 신호를 800ns마다

(a & b) | (c & d) 가 y_a 이므로 150ns에서 a & b 신호는 1, c & d 신호는 0이므로 | 에 의하여 1의 신호 출력

350ns는 (a & b) | (c & d) 이므로 350ns에서 1dml tlsgh

550ns에서 a & (b | c) & d 는 b | c = 1, a & (b | c)는 1, a & (b | c) & d = 1 따라서 550ns에서의 y_b신호는 1

wire는 다른 element들을 연결해주는 데 사용. 즉, 물리적인 연결선으로 다뤄지며 특정 값을 지정할 수는 없다. 그러므로 연속적인 할당으로 코드를 구현할 때 사용

또한, reg도 존재하는데 reg는 다음 값이 할당되기까지 현재 값을 유지한다. 그러므로 절차적 할당으로 코드를 기술할 때 사용된다. 만약 combination logic을 선언하는 것이 연속적인 할당이고 always, initial등의 문법을 사용하여 logic을 선언하는 것이 절차적 할당이다.

y_a는 (and_ab | and_cd)

y_b는 (a & d) & or_bc

and_ab는 a와 b가 1일 때 1을 출력하는 것을 확인할 수 있다.

and_cd는 c와 d가 1일 때 1을 출력하는 것을 확인할 수 있다.

or_bc는 b와 c 둘 중 하나라도 1일 경우 1을 출력한다.

y_a, y_b 또한 원하던 결과를 출력한다.

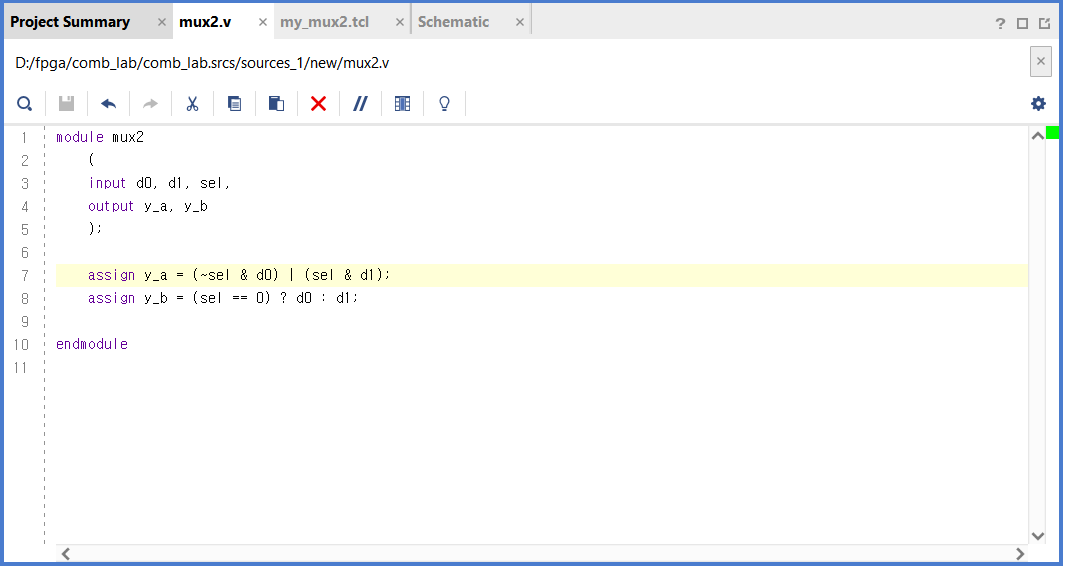

~는 not의 의미. y_a는 (~sel & d0) | (sel & d1), y_b는 (sel == 0) ? d0: d1.

y_a는 (~sel & d0) | (sel & d1), y_b는 (sel == 0) ? d0: d1.

y_a : ~sel 이기 때문에 400us까지 sel은 1이며 800us까지 sel은 0을 출력하는 상태이다.

따라서 y_a는 0~400us까지는 d0와 같은 신호를 출력하며 400~800us는 d1과 같은 신호를 출력한다.

y_b : sel == 0이면 d0과 같은 신호, sel이 0이 아닐 경우 d1과 같은 신호를 내보낸다.

원하는 결과값을 출력한다.

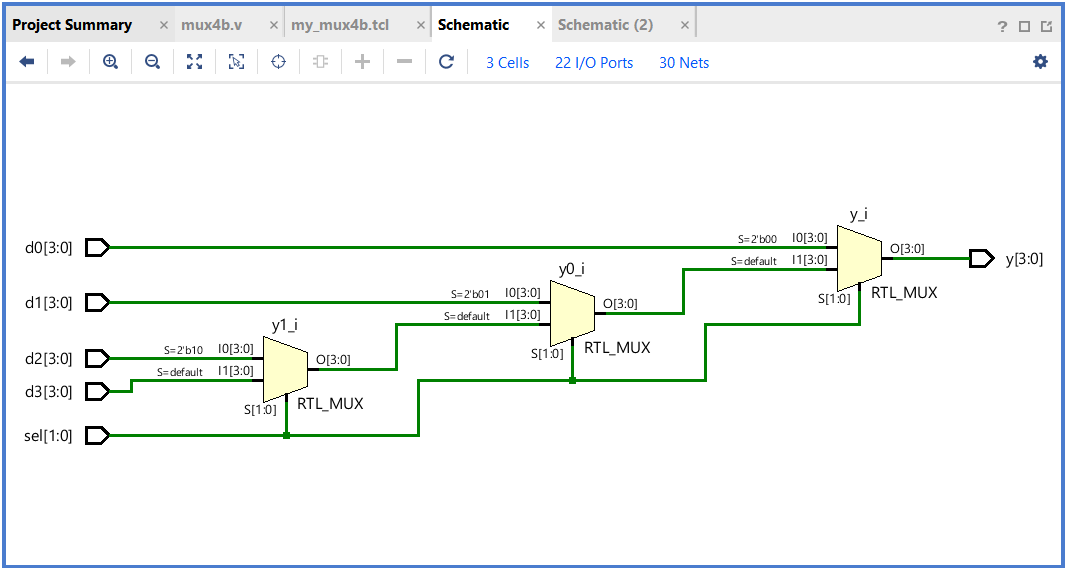

sel = 0이면 d0, sel = 1이면 d1, sel = 2이면 d2, 아무것도 아니면 d3을 출력한다.

sel = 0일 때 d0 3의 값을, sel = 1일 때 d1 6의 값을, sel = 2일 때 d2 9의 값을, sel = 3일 때 d3 c의 값을 출력하는걸 확인 할 수 있다.

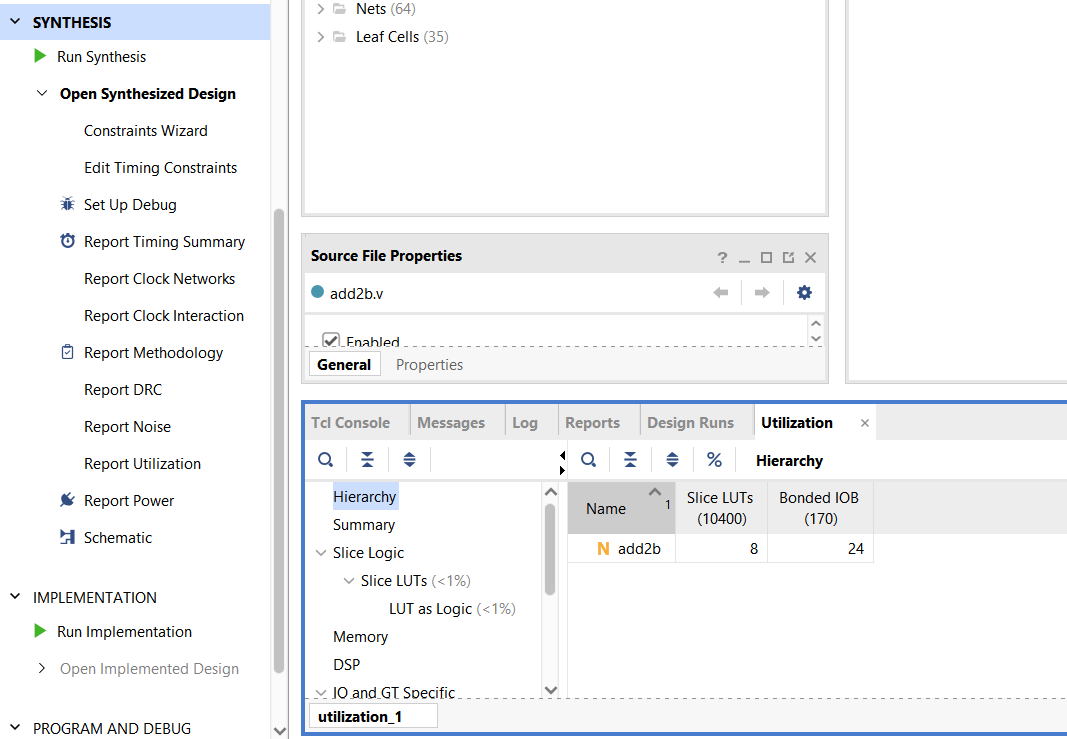

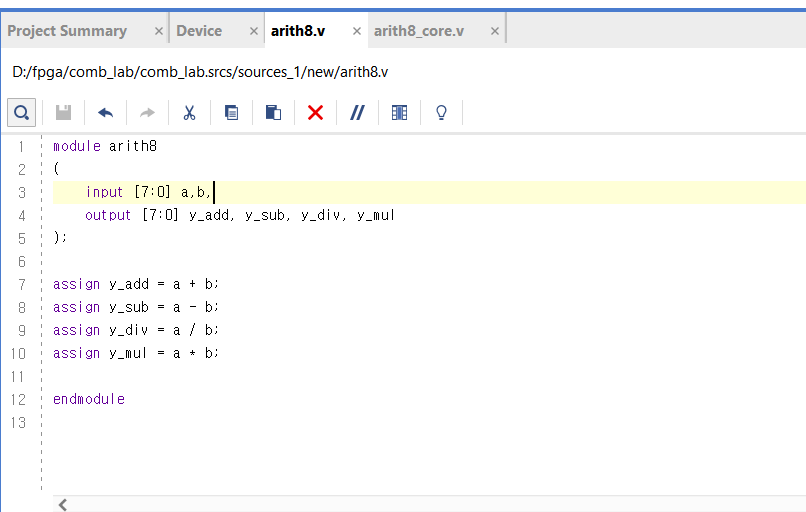

덧셈 연산 회로

assign y = a + b;

a + b 를 확인해보기위함.

carry chain = CARRY 4

Report Utilization 클릭

LUT 8개 사용

LUT 8개

버퍼 24개

CARRY CHAIN 2개

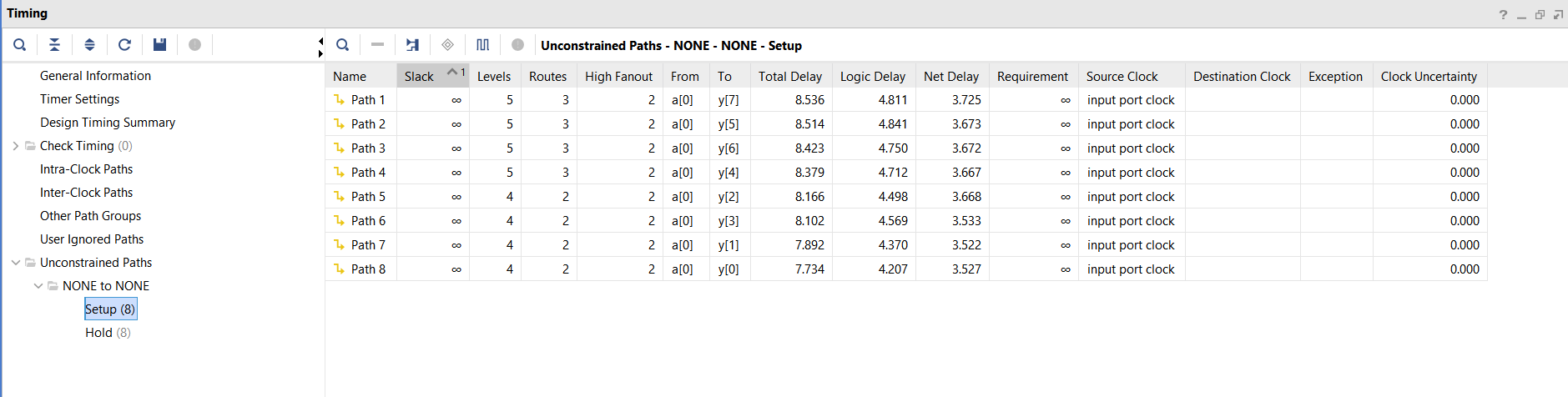

딜레이 확인은 report timing summary

Total delay : 8.536

Logic delay : 4.811

Net delay : 3.725

뺄셈 연산 회로

assign y = a - b;

덧셈 연산 회로와 같음

덧셈 연산 회로에는 overflow, 뺄셈 연산 회로에는 borrow

Total delay : 8.536

Logic delay : 4.811

Net delay : 3.725

덧셈 연산 회로랑 같은 결과

곱셈 연산 회로

assign y = a * b;

LUT 2 : 13개

LUT 3 : 2개

LUT 4 : 7개

LUT 5 : 2개

LUT 6 :16개

CARRY CHAIN : 6개

Total delay : 11.816

Logic delay : 5.620

Net delay : 6.196

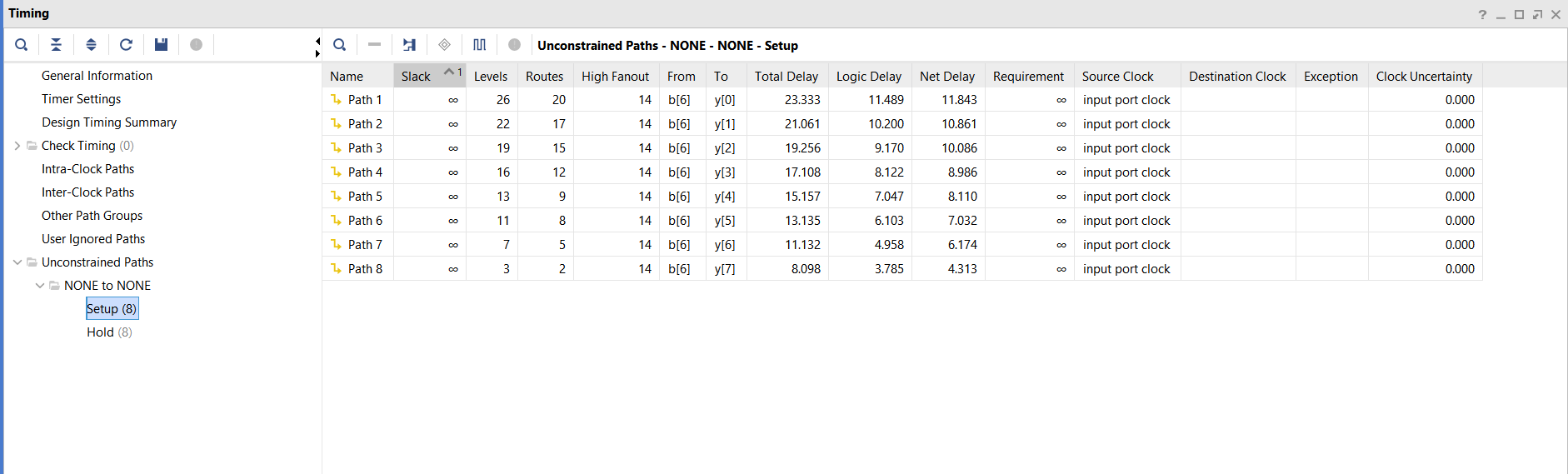

나눗셈 연산 회로

assign y = a / b;

LUT 2 : 13개

LUT 3 : 49개

LUT 4 : 7개

LUT 5 : 3개

LUT 6 : 3개

CARRY CHAIN : 21개

Total delay : 23.333

Logic delay : 11.489

Net delay : 11.843

DSP 45개 중 1개 사용

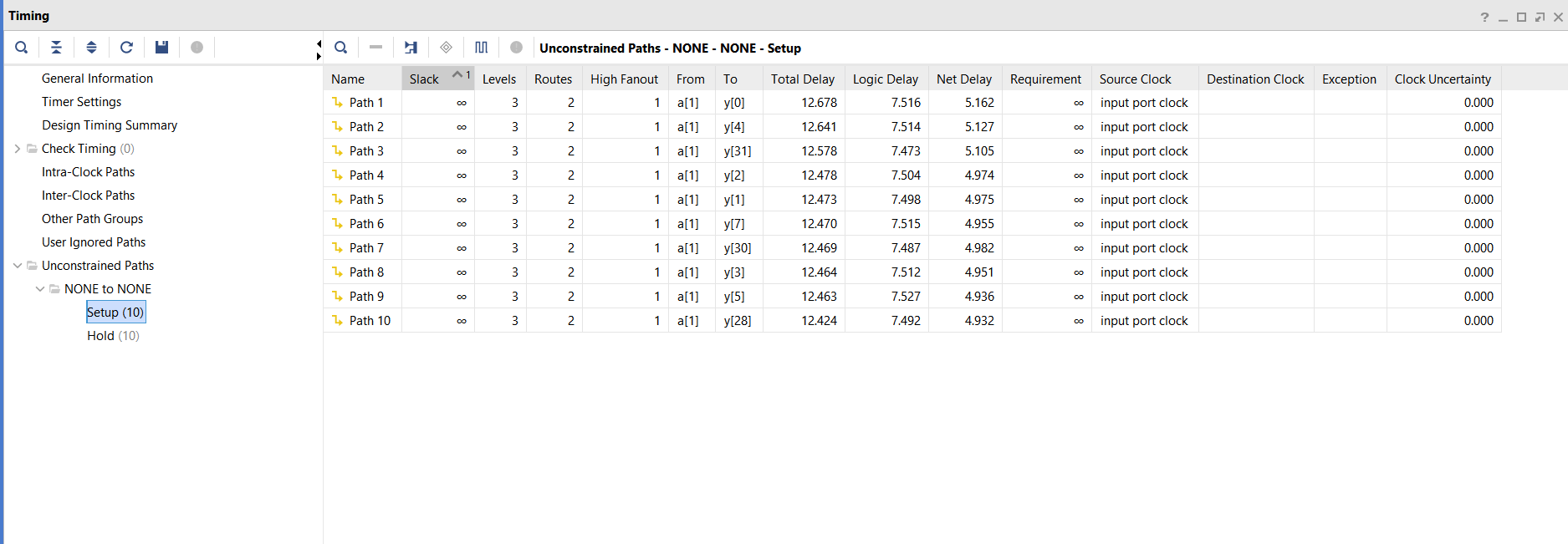

곱셈 연산 회로를 input[15:0], output[31:0] 한 결과

곱셈기로 16bit x 16bit 하니 delay가 너무 길어짐

DSP48E1 사용

DSP48E1 구조

mul x 16 x 16bit

Total delay : 12.678

Logic delay : 7.516

Net delay: 5.162

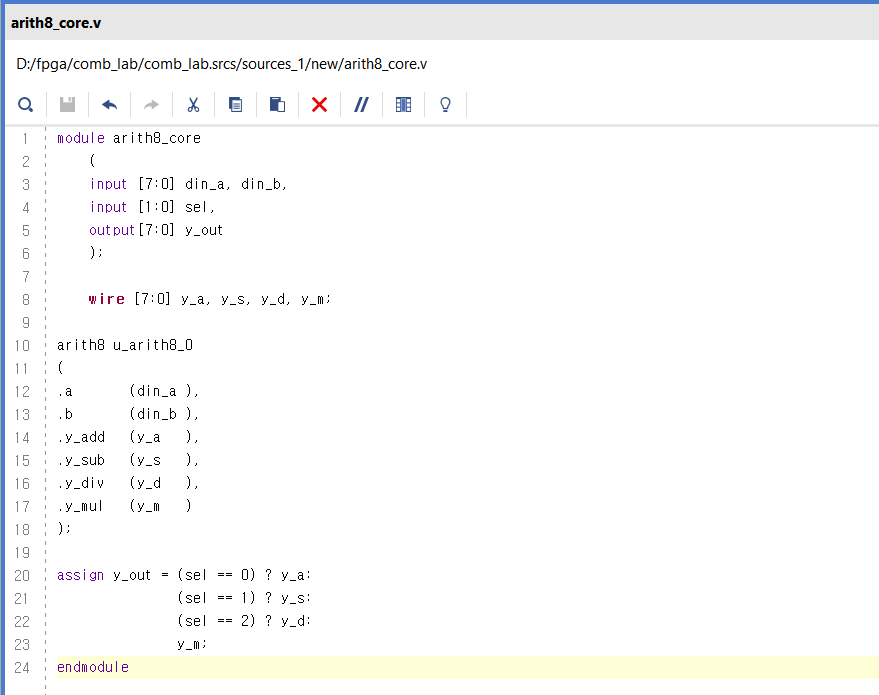

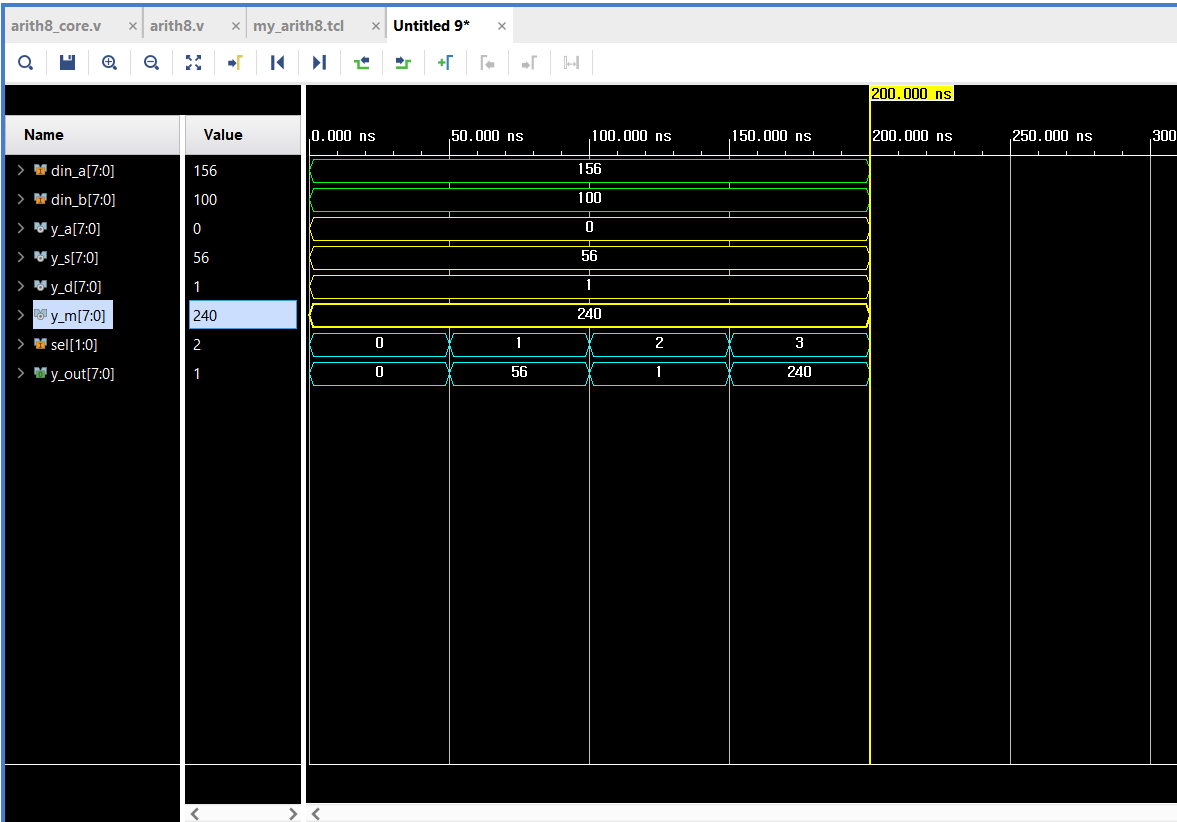

sel[1:0]과 y_out[7:0] 의 value가 교수님과 달라 물어보니 마우스 커서의 위치에 따라 달라진다.

현재는 sel 2, y_out 1 인 곳의 마우스 커서

현재는 1과 56의 마우스커서

캐리아웃

'Verilog' 카테고리의 다른 글

| Verilog 레지스터 (0) | 2023.04.26 |

|---|---|

| Verilog 멀티플렉서, BCD 변환기, 플립플롭 (0) | 2023.04.19 |

| Verilog 인코더, 디코더, 7세그먼트, 멀티플렉서 (0) | 2023.04.18 |

| Verilog 3일 특강 2 (0) | 2023.04.17 |

| Verilog 반가산기, 전가산기, 병렬가감산기, 비교기 (0) | 2023.04.17 |