Verilog 인코더, 디코더, 7세그먼트, 멀티플렉서

2비트 비교기

2bit 비교기를 만들 경우 [1:0], 16bit 비교기를 만들 경우 [15:0]

A, B가 0일 때 equal의 값이 1, A = 2, B = 0일 때 bigger 값이 1, A = 0, B = 2일 때 less값이 1.

디코더

디코더 : 입력선에 나타나는 n비트의 2진 코드를 최대 2^n개의 서로 다른 정보로 바꿔주는 조합논리회로

인에이블(enable) 단자를 가지고 있는 경우는 디멀티플렉서의 기능도 수행

실제 상용 IC의 경우에는 디코더와 디멀티플렉서의 기능으로 모두 사용

74138 : 3X8 디코더/디멀티플렉서

74139 : 독립된 2개의 2X4 디코더/디멀티플렉서

74154 : 4X16 디코더/디멀티플렉서

아래 코드 값들의 핀 번호와 갯수

A = 4개, B = 4개, S = 4개

Run Synthesis > Run implementation > Generate Bitstream 순으로 진행

Generate Bitstream 을 먼저 실행하면 자동으로 아래 항목들이 실행된다.

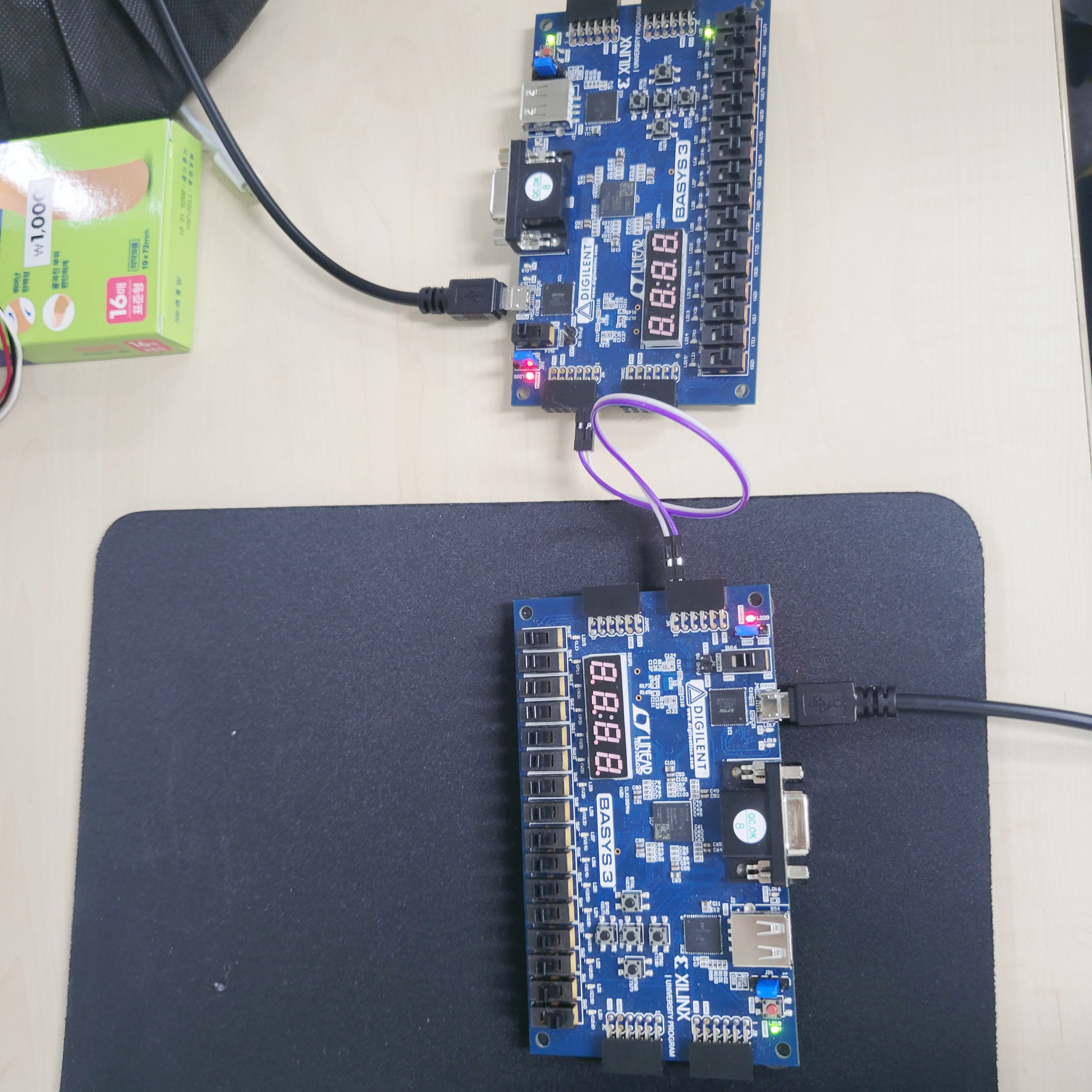

Basys3 동작확인

위 코드가 포함된 fadder_4bit코드 활용

A = 1, B = 1 LED는 이진법으로 2 출력

A = 2, B = 4 LED는 이진법으로 6 출력

A = 8, B = 8 LED는 16을 출력

Cin은 0으로 넣었기에 따로 쓰지않는다.

인코더

인코더는 디코더의 반대기능을 수행하는 장치이다. 2^n개의 입력신호로부터 n개의 출력신호를 만든다.

인코더의 역할은 2^n개 중 활성화된 하나의 1비트 입력신호를 받아서 그 숫자에 해당하는 n비트 2진 정보를 출력한다.

2x1 인코더

4x2 인코더

입력의 신호에 따라 2개의 2진 조합으로 출력된다.

2X4 디코터

2개의 입력에 따라서 4개의 출력 중 하나가 선택

아래 코드는 A와 B를 A0, A1로 정의함

인코더 시뮬레이션

D의 입력은 D0, D1, D2, D3로 BUS지정으로 0~3까지 정의

B의 출력은 B0, B1으로 BUS지정으로 0, 1을 정의

시뮬레이션을 위한 코드 작성을 위해

Add sources를 선택하여 sim1에 encoder_4_2_tb 파일을 추가로 작성한다

들어오는 신호를 reg로 받고, 나가는 신호를 wire로 받는다.

#1000dms 위에 time scale이 1ns이기 때문에 단위는 ns이며, D=4'b0001, 0010, 0100, 1000이 1000ns동안 어떻게 작동하는지 확인.

ns단위로 시뮬레이션을 하되, 시뮬레이션은 1ps까지 진행된다.

$finish는 시뮬레이션의 종료를 의미한다.

D 0001일 때 B는 00

D 0010 일 때 B는 01

D 0100 일 때 B는 10

D 1000 일 때 B는 11

표의 값과 시뮬레이션의 값이 일치하는걸 확인할 수 있다.

디코더 시뮬레이션

기존에 진행했던 디코더 코드에

시뮬레이션을 위한 코드를 작성하여

A = 00, 01, 10, 11 일 때의 결과를 시뮬레이션으로 확인한다.

2'b00 일 때 0001

2'b01 일 때 0010

2'b10 일 때 0100

2'b11 일 때 1000

표의 값과 시뮬레이션의 값과 일치함을 확인할 수 있다.

Basys3 을 상대방과 연결하여 내 Basys3에는 encoder의 코드, 상대에게는 decoder의 코드를 입력

나는 JA1, 2 상대는 JB1, 2에 연결하였다.

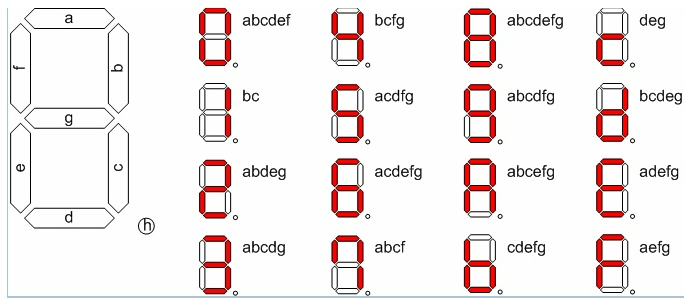

BCD-7-세그먼트 디코더

7세그먼트 : 숫자 표시 전용 디코더

애노드 방식, 캐소드 방식

7세그먼트 입력, 출력

0000 = 0, 0001 = 1, 0010 = 2, 0011 = 3, A, F는 5번째 올렸으나 상관 없는 스위치 전부 코드와 일치하게 나옴

나는 세그먼트에 com_an을 사용해 0을 입력해서 전부 켜지게 작동시켰다. (D0, D1, D2, D3)

anode방식이다.

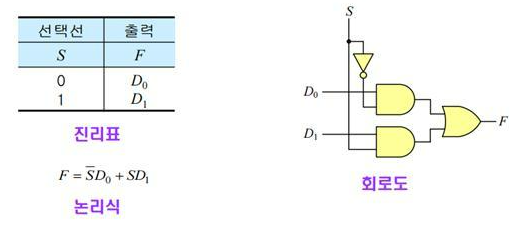

멀티플렉서

2X1 멀티 플렉서

2(2=2^1)개의 입력 중의 하나를 선택선 S에 입력된 값에 따라서 출력으로 보내주는 조합회로

d0는 Sbar와 연결 되어있으니 Sbar, d0의 and 신호가 출력된다.

d1은 S와 연결 되어있어 S, d1의 and 신호가 출력된다.